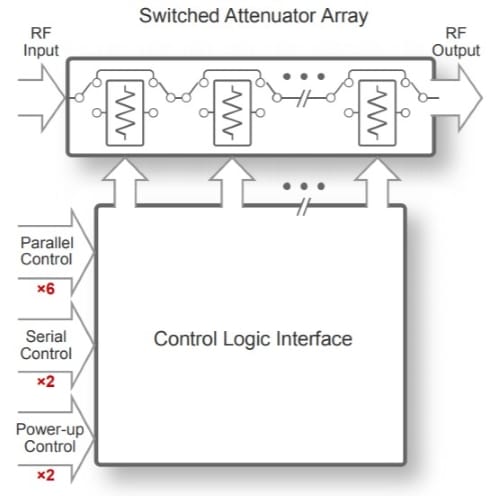

The PE43665 is a 75Ω, high-linearity, 6-bit RF digital step attenuator (DSA) covering a 31.5 dB attenuation range in 0.5 dB steps. The PE43665 provides both a parallel (latched or direct mode) and serial CMOS control interface, operates on a single 3V supply and maintains high attenuation accuracy over frequency and temperature. It also has a unique control interface that allows the user to select an initial attenuation state at power-up. The PE43665 exhibits very low insertion loss and low power consumption. This functionality is delivered in a 4 × 4 mm QFN footprint.